Keeping you up-to-date, everytime

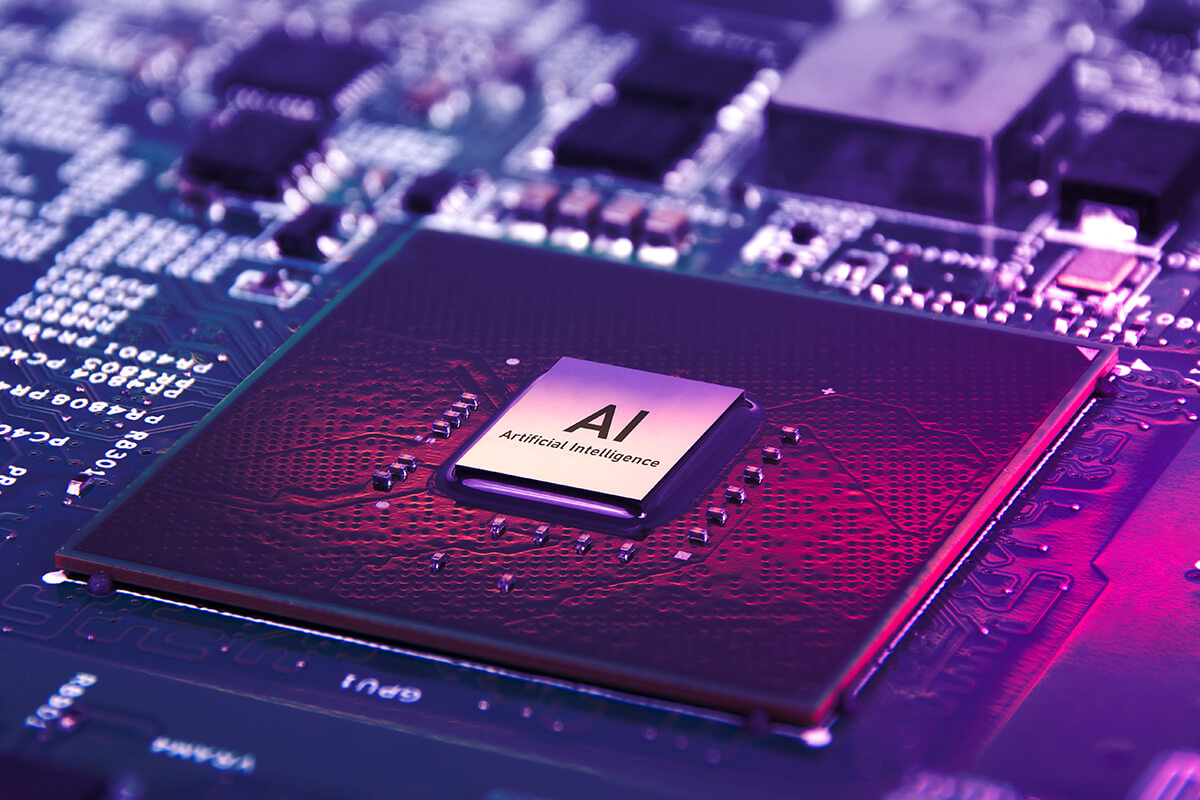

Hero Electronix, the parent company of Tessolve, launched another brand under its umbrella last week. The new brand – Qubo – will launch a series of AI-powered intelligent home appliances,…

Hero Electronix, the parent company of Tessolve, launched another brand under its umbrella last week. The new brand – Qubo – will launch a series of AI-powered intelligent home appliances,…