A HERO ELECTRONIX VENTURE

### Webinar 3: AI Assisted Advanced DV Flow & Use cases 😭

#### Mike Bartley, SVP, CoE | Marmik Soni, Sr. Design Lead, CoE

### Outline

- 1: UVM AI Training Tool

- 2: Basic TB Generation Tool

- 3: Automating Coverage Closure

- Collaboration Opportunity

### AI Ecosystem

#### Knowledge Bots:

- Features: Faster to develop & deploy

- Use case: With less confidential data, Project CoPilot

- Security: Low

- Cost: Low

- Reasonable accuracy,

- **Project:** UVM Chatbot, FUSA Chatbot

#### Build: Cloud Deploy: Cloud/ Hosting Services

- Feature: Faster develop & deploy

- Use case: Client projects, highly confidential data.

- Security: High

- Cost: High

#### Build: Local Deploy: Local

- Features: Slower to develop & slower to deploy

- Use case: For highly confidential data

- Security: High

- Cost: High

- Challenge: Less Adaptability, less Scalability, Upfront Cost

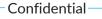

#### Al-Auto Agents / Apps

- DV Spec Extraction Tool

- UVM TB Automation

- Assertify tool

- Al code copilots

- Al Training Tools, FUSA, PDK, **UVM** etc.

- Basic TB Generator

- Automating Coverage Closure

3

©Tessolve 2024

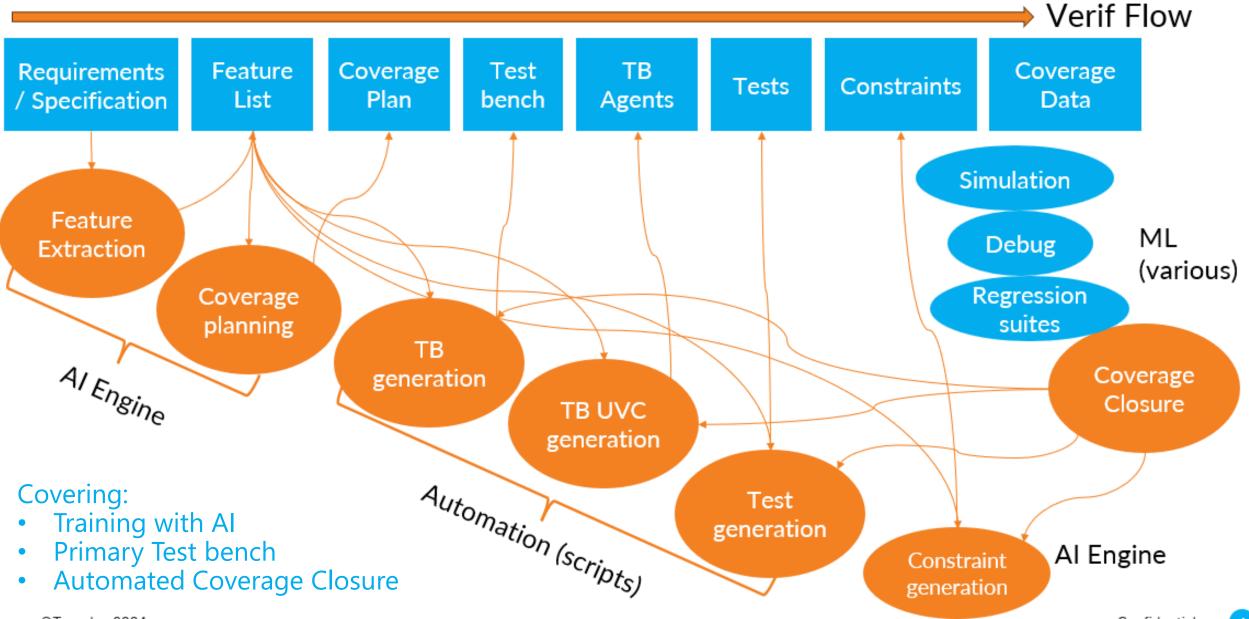

### AI/ML Experiments in IP Verification

A HERO ELECTRONIX VENTURE

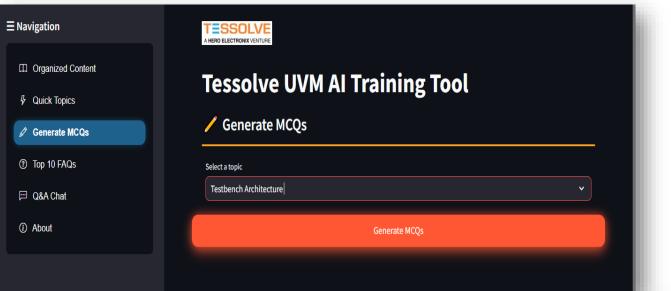

#### **Organized Content**

• Follows planned flow

#### **Quick Topics**

• Most important topics' explanation

#### MCQs

• Test, Evaluation, weak concept suggestions

#### FAQs

• Clarifies on common important doubts

#### Q&A

• ANY question support

#### About

• Tool briefing for effective use

#### **Benefits:**

- Self guided and self paced flow

- Analytics & custom topic suggestions

- Ask anything about UVM

- Improved accessibility

- Reduced training time

- Scalable for other domains

## **Tessolve UVM AI Training Tool**

#### $\equiv$ Navigation

#### Quick Topics

⑦ Top 10 FAQs

💬 Q&A Chat

About

#### Deploy Organized Content Select a section from the index UVM Basics $\sim$ Summarize **UVM Basics Summary** Introduction to UVM Universal Verification Methodology (UVM) is a standard developed by Accellera, integrating contributions from various methodologies (OVM, eRM, VMM).

©Tessolve 2024

Confidential

| Generate MCQs                                                                       | Quick Topics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |                                          |  |  |  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------|--|--|--|

| ⑦ Top 10 FAQs                                                                       | UVM Sequence Items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Generating Stimulus                        | Overriding Sequences                     |  |  |  |

| 💬 Q&A Chat                                                                          | Integrating a UVM Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UVM Sequences                              | Driver-Sequence API                      |  |  |  |

| <ol> <li>About</li> </ol>                                                           | Sequence API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Analysis Components                        | Configuring Sequence                     |  |  |  |

|                                                                                     | UVM Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Building a UVM Testb                       | Messaging in Sequenc                     |  |  |  |

| <ul> <li>✓ Deploy</li> <li>■ Navigation</li> <li>UVM Sequences</li> </ul>           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |                                          |  |  |  |

| <ul> <li>Corganized Content</li> <li>Quick Topics</li> <li>Generate MCQs</li> </ul> | <b>Introduction</b><br>UVM (Universal Verification Methodology) sequences are a pivotal aspect of transaction-level stimulus generation used in<br>verification environments. They provide an object-oriented approach to creating and managing test scenarios, allowing for<br>efficient, flexible, and reusable stimulus generation. UVM sequences are designed to promote abstraction, enabling test<br>writers to generate complex tests without being tightly coupled to specific testbench components. |                                            |                                          |  |  |  |

| <ul> <li>⑦ Top 10 FAQs</li> <li>□ Q&amp;A Chat</li> <li>③ About</li> </ul>          | Main Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | initiated using the uvm_sequence start() n | nethod. which links them to a sequencer. |  |  |  |

| ©Tessolve 2024                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            | Confidential —                           |  |  |  |

| <                   |                                                                                                                   | Deploy :            | Deploy                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------|

| lavigation          | MCQs for Testbench Architecture:                                                                                  | <b>≡</b> Navigation | X Question 5: Incorrect.                                                           |

| lavigation          | Question 1: What does the Dual Top testbench architecture separate?                                               | = Navigation        | Your answer: Option A: To generate stimulus transactions                           |

|                     | Select an option:                                                                                                 |                     |                                                                                    |

| D Organized Content | (A) Timed signal level code and transaction level testbench code                                                  | Organized Content   | Correct answer: Option B: To collect transactions and perform comparative analysis |

| Quick Topics        | (B) Design Under Test (DUT) and verification environment                                                          | ₿ Quick Topics      | Recommended topic to review: Analysis Components & Techniques                      |

|                     | <ul> <li>(C) Static and dynamic components</li> <li>(D) Hardware and software components</li> </ul>               |                     |                                                                                    |

|                     |                                                                                                                   | 🖉 Generate MCQs     |                                                                                    |

| D T 40 FAO-         | Question 2: What is the role of the BFM interface in the testbench architecture?                                  | ⑦ Top 10 FAQs       |                                                                                    |

| ) Top 10 FAQs       | Select an option:                                                                                                 | () TOP TO FAQS      | Your Score: 1 / 5                                                                  |

| 🗉 Q&A Chat          | (A) To handle transaction level code                                                                              | 💬 Q&A Chat          |                                                                                    |

|                     | (B) To manage signal level code                                                                                   |                     |                                                                                    |

| About               | <ul> <li>(C) To connect the DUT to the testbench</li> <li>(D) To facilitate inter-domain communication</li> </ul> | ① About             | Review the incorrect answers and recommended topics to improve your understanding. |

|                     |                                                                                                                   |                     |                                                                                    |

|                     | Question 3: In the UVM testbench build process, what is the first phase?                                          |                     |                                                                                    |

|                     | Select an option:                                                                                                 |                     |                                                                                    |

|                     | (A) Run phase                                                                                                     |                     |                                                                                    |

|                     | (B) Configuration phase                                                                                           |                     | 💉 Developed by AI CoE team                                                         |

|                     | 💉 Developed by Al CoE team                                                                                        |                     |                                                                                    |

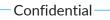

### 2: Simple TB Generation – Independent Verification for Designers

- There is always a need for designers to have a basic test bench to make sure the RTL is basically functional before handing it to verification.

- But there is a concern for independence otherwise designers are just verifying their understanding a single point of failure.

- We demonstrate our tooling that can generate simple test bench from the specification either in Verilog or SV

- if preferred by the designer

- or basic UVM if they prefer

- Designers can add "designer knowledge" to their generated test bench

- For example:

- Assertions

- functional coverage

- A scoreboard function (test bench hooks can be given for that)

- Verification engineers can decide if they want to reuse them

- With full knowledge of any associated risks

Confidential — 10

Deploy :

#### Tessolve Unit TB Generation & Simulation Tool is designed to automate the creation and refinement of Verilog testbenches. This application simplifies and accelerates the process of generating and debugging testbenches, providing you with multiple iterations.

New Design 🔤

About

#### **Edit Testbench Code** Edit Testbench Code `timescale 1ns/1ps module LFSR\_8bit\_tb; reg clk; reg rst\_n; wire [7:0] Q; LFSR\_8bit uut ( .clk(clk), .rst\_n(rst\_n), .Q(Q) ); initial begin \$dumpfile("waveform.vcd"); \$dumpvars(0, LFSR\_8bit\_tb); end initial begin 💋 Developed by CoE Team

#### 📕 About

Tessolve Unit TB Generation & Simulation Tool is designed to automate the creation and refinement of Verilog testbenches. This application simplifies and accelerates the process of generating and debugging testbenches, providing you with multiple iterations.

New Design 🚾

# Tessolve Unit TB Generation & Simulation Tool

| D Upload Module           | 📥 Edit Testbench               | Compilation | Simulation |  |  |  |  |

|---------------------------|--------------------------------|-------------|------------|--|--|--|--|

| X Compilation             |                                |             |            |  |  |  |  |

| Compilation successful! 🎉 |                                |             |            |  |  |  |  |

|                           | **Go to the Simulation tab** 🔫 |             |            |  |  |  |  |

|                           |                                |             |            |  |  |  |  |

| 💋 Developed by CoE Team   |                                |             |            |  |  |  |  |

A quick first cut basic SV testbench generation tool to help designers to get easy debug of the RTL.

#### **Features:**

- AI TB generation

- Error feedback

- Tool chain Integration for compilation, simulation

#### **Benefits:**

- Error handling

- Accelerate designer "smoke test" verification

- No need to involve DV

- Time saving

- Tool integration saves lot of time

- Opensource tool set

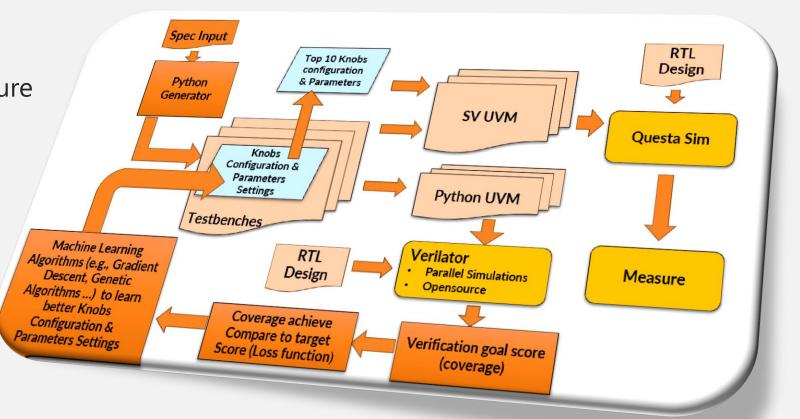

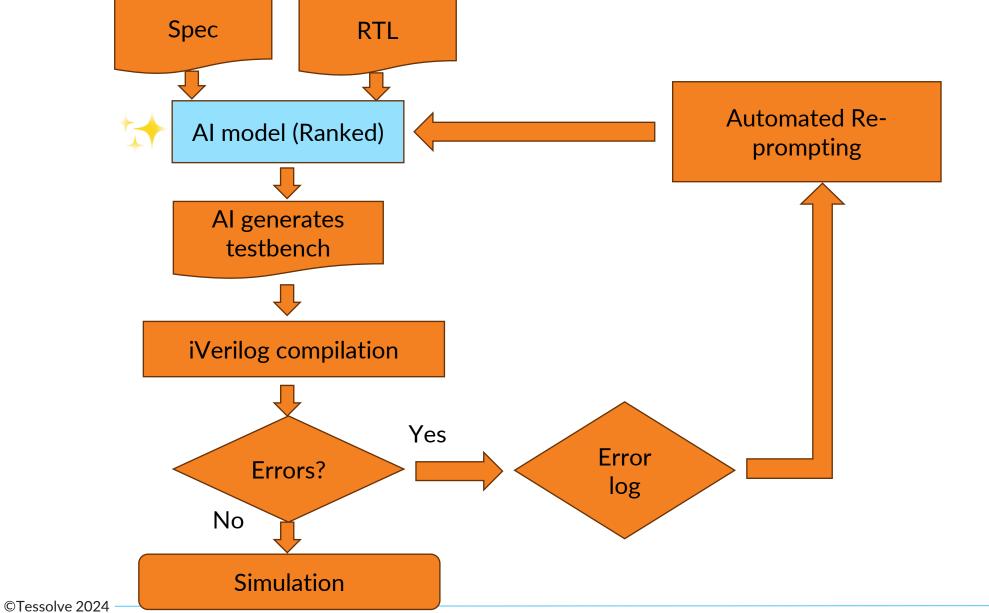

### 3: Automating Coverage Closure – The Ultimate Objective

Achieving coverage closure in verification is challenging, consuming up to 80% of efforts. Automation in this area remains a formidable challenge. Tessolve leverages AI to automate this process effectively.

#### **Benefits:**

- Reduced verification

efforts

- Fast opensource simulation

- High efficiency feedback loop

- Complete automation

#### Python UVM Test Bench Generation:

• Generation of test bench with numerous "knobs and hooks" to configure the constrained random generation.

#### Intelligent AI agents:

• By intelligent AI agents and employing a suitable loss function, we guide the system towards the coverage goal.

#### Machine Learning Techniques:

• Techniques such as gradient descent or genetic algorithms are employed by ML to achieve the desired coverage.

#### Simulation Strategy:

• Multiple simulations are crucial for the ML model to learn effectively. We demonstrate the use of a Python test bench with Verilator for quick, cost-effective simulations before transitioning to System Verilog (SV) with a recognized simulator for signoff. This approach helps mitigate the risk of different randomization outcomes.

©Tessolve 2024

### Why Python for TB Generation?

- We can still generate better test benches compared to AI

- Re-use of previous generation via config files per design

- E.g. re-use of previous test bench structures such as complex scoreboards

- Python knows the split between static and dynamic UVM structures

- Richer set of "knobs, config, and parameters"

- All collected in a separate file to help the ML learning process

- But under constant review and adding specific AI solutions

- Add AI for assertion generation

- And functional coverage generation

### **Collaboration with DV Flow**

A HERO ELECTRONIX VENTURE

### **Collaboration with AI Research**

### Webinar Series Summary

# **TESSOLVE**

A HERO ELECTRONIX VENTURE

# **THANK YOU**

https://calendly.com/mike-bartley-tessolve/one-one-call

www.tessolve.com

mike.bartley@tessolve.com

+44 7796 307958

Chip

Ŕ

Test Engineering Design

Hardware Design